The Next Generation of Arm Server CPU Cores

Just under four years ago, Arm announced the Neoverse family of infrastructure CPU designs. We decided to power the server and edge computing market by designing Arm CPU cores specifically for these markets, not only reusing our consumer-focused Cortex-A design, but also Arm has set out to tackle the infrastructure market in a much more aggressive way. These efforts have paid off more and more for Arm and its partners. Arm and its partners have finally managed to capture a meaningful portion of the server CPU market thanks to products such as his Graviton and Ampere Altra CPUs from Amazon.

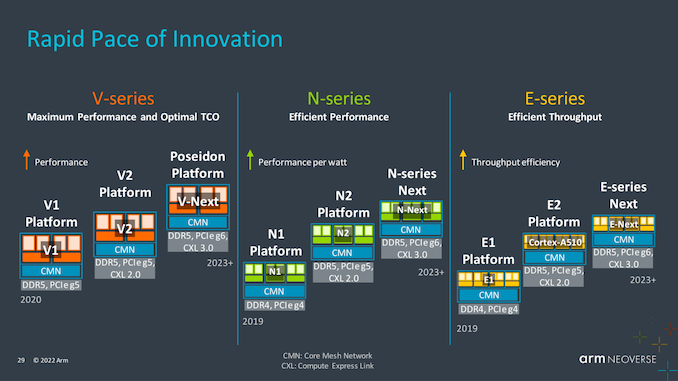

But as Arm CPUs finally achieve the market penetration they haven’t achieved in the last decade, we have to make sure that Arm isn’t resting on its laurels. Of the company’s three Neoverse core design lines (Efficient E, Flexible N, and High Performance V), the company is already using the second-generation N cores, aptly called N2. Now the company is preparing to update the rest of his Neoverse lineup with next-generation V and E cores and today announced the Neoverse V2 and Neoverse E2 cores. Both of these designs will bring the Armv9 architecture to his HPC and other server customers with significant performance gains.

Arm Neoverse V2: Armv9 Supports High Performance Computing

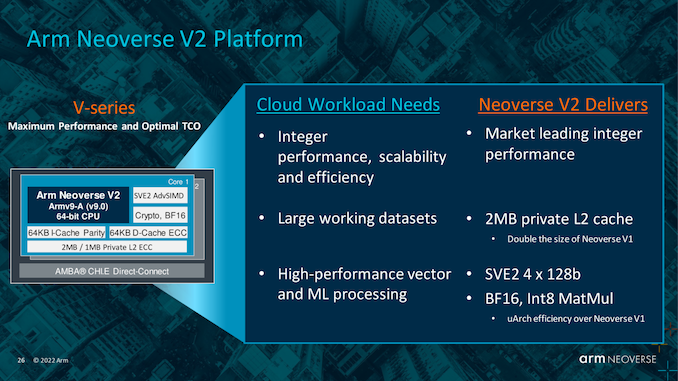

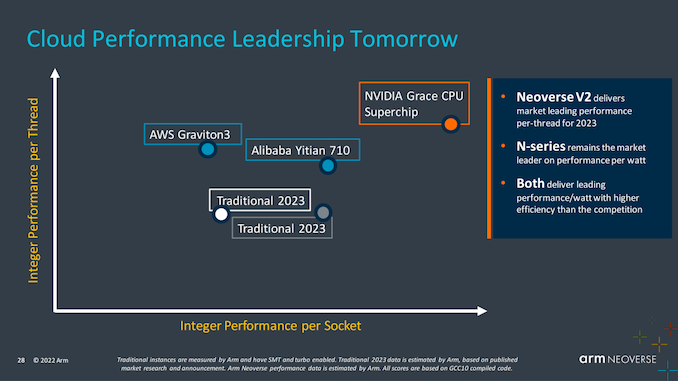

Spearheading Arm’s new CPU core IP is Neoverse V2, the company’s second-generation V-series design. The full V2 platform, codenamed Demeter, is Arm’s first iteration on its high-performance V-series cores, marking the transition of this core lineup from Armv8.4 ISA to Armv9. This is his second time Arm has committed to a high-performance core dedicated to servers, but make no mistake, Arm is aiming to be ambitious. The company claims that the Neoverse V2 CPUs will offer the best single-threaded integer performance available on the market, outperforming both AMD and Intel’s next-gen designs.

This week’s announcement from Arm isn’t full details of the new architecture, and more troublingly, the company isn’t talking about specific PPA metrics, but Arm does outline some changes and features. . It comes with the V2 platform. Sure, the V2 IP is already finished and shipping to customers (especially his NVIDIA) today, but Arm wants to see what they say about V2 before shipping its first IP-based chip in 2023. I am somewhat ashamed that I am

First and foremost, the bump to Armv9 brings the full suite of features that come with the latest Arm architecture. This includes Arm’s new SVE2 vector extensions as well as improvements to security, a fundamental feature of the architecture (especially useful in cloud shared environments).

For the latter, Arm makes an interesting change by reconfiguring the width of the vector engine. V1 used 2-pipeline 256-bit SIMD and he implemented SVE(1), but V2 moves to 128-bit SIMD 4-pipe. The net result is that the cumulative SIMD width of V2 is not wider than V1, but the execution flow is changed to process more small vectors in parallel.This change makes the SIMD pipeline width the same as Arm’s Cortex parts (all 128-bit, SVE2 smallest size), but Arm no longer scalable Configure part of the SVE with a larger SIMD. After Arm looks at the full details of his V2, we expect it to become clear why they’re going this route. I’m curious if this is purely for efficiency, or if it’s akin to homogenizing designs across the Arm ecosystem.

Beyond that, note that Arm’s presentation slides show bfloat16 and int8 matmul as features, but they are not. new feature. Still, Arm promises that V2’s SIMD processing will make the microarchitecture more efficient than V1.

More broadly, V2 also introduces a larger L2 cache size. The V2 design supports up to 2MB of private L2 cache per core. This is twice the maximum size of V1. V2 will also further improve Arm’s integer processing performance, but we haven’t covered the details at this time. From an architectural point of view, the V1 borrows quite a bit from the Cortex-X1 CPU design and it wouldn’t be too surprising if his V2 case borrowed from the X2 holds true again. In that case, consumer chips like the Snapdragon 8 Gen1 and Dimensity 9000 should provide a rough reference of what to expect.

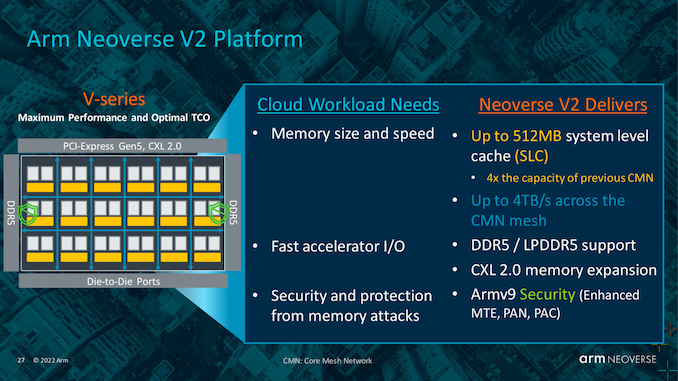

For the Demeter platform, Arm reuses the CMN-700 mesh fabric first introduced in the V1 generation. CMN-700 is a modern mesh design supporting up to 144 nodes in a 12×12 configuration, suitable for interfacing with PCIe 5/CXL 2 for DDR5 memory and I/O. As a result, strictly speaking, V2 brings nothing new at the fabric level. Even a 512MB SLC can run on a V1 + CMN-700 setup. But this is the baseline the CMN-700 mesh and its capabilities are currently moving forward with V2.

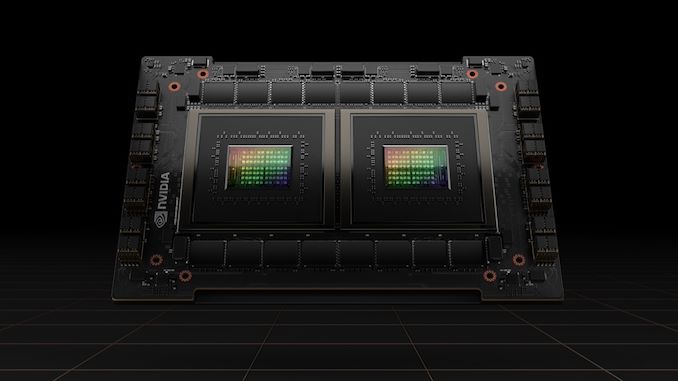

Next, Neoverse V2 cores will be the foundation for the next generation of high-performance Arm server CPUs. The de facto flagship here is NVIDIA’s Grace CPU which would be one of his first (if not the first) V2 designs to ship in 2023. Arm has finally confirmed long-standing suspicions that Grace is based on the next-generation Neoverse V core.

NVIDIA will be holding its Fall GTC event in the next few days. So with NVIDIA looking to promote the chip ahead of next year’s release, we’re likely to hear a little more about Grace and her Neoverse V2 underpinnings.

Neoverse E2: Cortex-A510 for use with N2

In addition to announcing Neoverse V2, Arm is using this week’s briefing to announce its Neoverse E2 platform. Unlike the V2 reveal, this is a much smaller announcement, with Arm providing only a handful of technical details. will come

However, the E2 platform is offered to partners for interoperability with existing N2 platforms. For this, Arm combined the Cortex-A510 CPU, Arm’s small/high efficiency Cortex CPU core, and combined it with the CMN-700 mesh. This is intended to give server operators/vendors more flexibility by offering alternative CPU cores to N2 while offering the latest I/O and memory capabilities of Arm’s mesh. To underscore this, the E2 system backplane is also compatible with his N2 backplane.

Neoverse Next: Poseidon, N-Next, E-Next

Finally, Arm’s announcement this week gives us a glimpse of the company’s future roadmap for all three Neoverse platforms. Naturally, Arm is working on updated versions for each platform.

In particular, all three platforms should add support for PCIe 6 and support for CXL 3.0. This comes from Arm’s next iteration of his CMN mesh network. This is shared across all three platforms, as Arm is already doing today.

On the other hand, it’s interesting to see Poseidon’s name return to Arm’s roadmap.Back to Arms First Neoverse Roadmap, Poseidon is the name given to Arm’s 5mn/2021 platform and has been spot on since it was variously adopted by N2 and V1/V2. Poseidon/V3 is still a few years away as V2 he won’t be in hardware until 2023, but it would seem that Arm’s keeping the codename means something (new microarchitecture, etc. ).

But first comes the N-Next platform, possibly the Neoverse N3. The Neoverse N platform is a generation ahead of the rest (N2 was first announced in 2020) and will be our next updated platform. The N3 is expected to be available to his partners in 2023, with Arm widely touting performance and efficiency improvements across generations.