Arm Unveils 2023 Mobile CPU Core Designs: Cortex-X4, A720, and A520

If there’s one universal constant in the global smartphone and mobile device market, it’s Arm. Whether mobile chip makers are adopting SoCs based on Arm’s fully synthesized CPU cores, or simply relying on Arm ISA to design their own chips, at the end of the day, effectively All foundations are in Arm. This kind of market saturation and relevance is a testament to all the efforts Arm has made over the last few decades to get here, but it is also a huge responsibility. Most mobile SoCs only scale their performance at a fixed speed. It uses Arm’s own CPU core design and associated IP.

As a result, we’ve seen Arm settle on an annual pace of client IPs, and this year is no exception. In line with this year’s Computex trade show in Taiwan, Arm is showing off a new set of Cortex-A and Cortex-X series CPU cores as well as a new generation of GPU designs. Arm will launch later this year through 2024. This includes his Cortex-X4 core on the flagship and Arm’s mid-core Cortex-A720. And a new small core Cortex-A520.

Arm’s latest CPU cores are built on the foundation of Armv9 and its Total Compute Solutions (TSC21/22) ecosystem. Heading into its 2023 IP, Arm is rolling out a wave of microarchitectural improvements through its Cortex coreline with subtle changes designed to improve overall efficiency and performance, while simultaneously fully Migrating to his AArch64 64-bit instruction set. Arm’s latest CPU designs are aligned with the industry-wide ongoing movement towards increased security, and while these features aren’t strictly for the end user, Arm’s generational improvements It emphasizes more than just performance and power. efficiency.

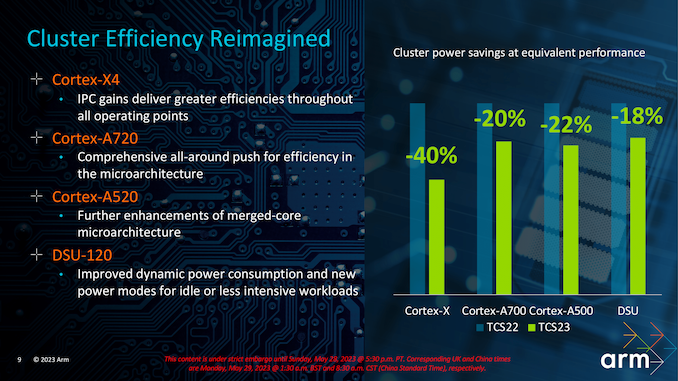

In addition to the CPU core improvements, Arm has also performed a comprehensive upgrade of the DynamIQ shared unit core composite block with the DSU-120. The changes introduced are subtle, but significant in terms of improving the efficiency of the fabric that holds Arm CPU cores together, and by supporting up to 14 CPU cores in a single block. It further expands Arm’s reach in terms of performance scalability. – A move designed to make Cortex-A/X even more suitable for laptops.

With three new CPU cores and a new core complex, there’s a lot to cover. Let’s jump in.

High-Level Enhancements to TCS23: Increased Efficiency and Transition to Pure 64-Bit

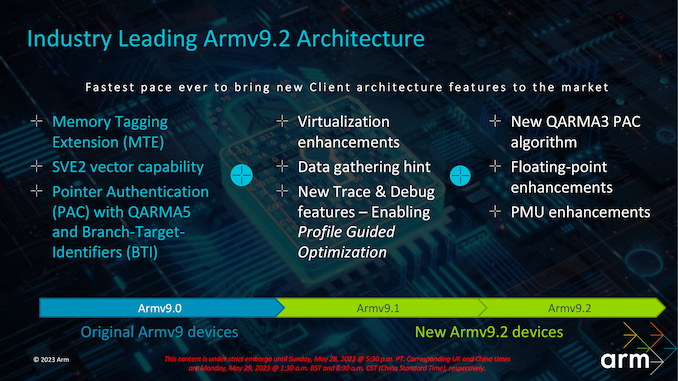

Building on the enhancements introduced last year with the Armv9.1 architecture, Arm is moving forward with its planned development cycle with its latest Armv9.2 architecture. The primary goal of this cycle is to drop support for 32-bit applications and move to a comprehensive 64-bit platform. Underpinning this transition is Arm’s strategic framework ‘Total Computing Solutions’ (TCS) centered around his three core principles of computing performance, security and developer access. This approach forms the foundation of Arm’s methodology and guides our efforts to achieve optimal performance, robust security measures and streamlined development capabilities.

Arm has been working on phasing out the 32-bit instruction set for several years. With the latest TCS23, we have finally created a full 64-bit cluster that completely removes support for AArch32 (32-bit instructions) to take full advantage of a full 64-bit mobile ecosystem. There are very few cores and Arm’s latest generation of IP only has AArch64.

Developing dynamic system-on-chips (SoCs) for a wide range of mobile devices, from cutting-edge flagship smartphones to entry-level models, requires close attention to remain competitive in a rapidly expanding market. You need a consistent approach that pays for For example, in the flagship device space, Qualcomm’s Snapdragon 8 Gen2 SoC stands out, leveraging Arm’s cluster of Cortex-X3, Cortex A715/710, and Cortex-A510 cores. Qualcomm’s upcoming versions of his Snapdragon 8 Gen3 and other his SoC makers are poised to leverage the power of Arm’s TSC23 core cluster and intellectual property to further boost the performance of their next-generation flagship mobile devices. it’s finished.

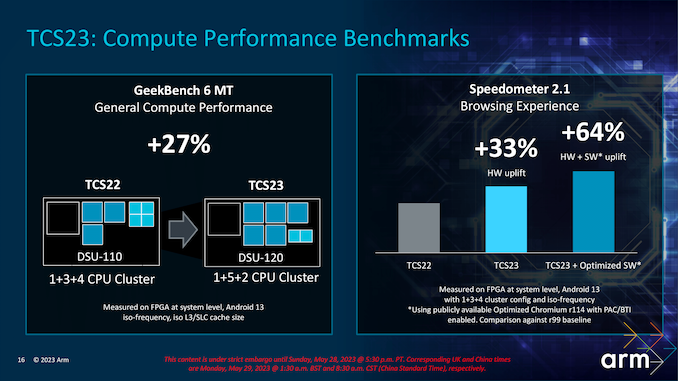

Arm’s latest DynamIQ shared unit, the DSU-120, supports up to 14 CPU cores in a cluster, opening the door to many different CPU core combinations. Later this year he’ll see what SoC vendors choose, but perhaps one of the configurations is 1+5+2 (X4+720+520) which is probably meant for higher end smartphones Configuration. Compared to his 1+3+4 cluster (X3+715+510) in the previous generation, Arm sees a 27% improvement in computing performance for his GeekBench 6 MT, and an additional 33% to 64% improvement on the speedometer. Claims a significant improvement. 2.1 Benchmarks rely on implemented software optimizations.

Last year, Arm put more emphasis on its approach to the 64-bit transition, announcing its first AArch64-dedicated CPU core, the Cortex-A715. As a result, last year saw the release of his first 64-bit only products, including MediaTek’s Dimensity 9200 SoC and Google’s Pixel 7. This was not an architectural limitation, he was 64-bit only as a platform choice.

That said, the actual adoption/usage of AArch64 within the large software ecosystem has been slower than expected, mainly due to the slow switch from 32-bit to 64-bit in the Chinese market. In fact, Google has held the key to application storage (Google Play) by requiring developers to submit 64-bit apps in his 2019, while his It also allowed the use of 32-bit applications in Other markets haven’t responded as quickly, but Arm claims it’s “pushing” companies like OPPO, Vivi and Xiaomi to adopt AArch64 sooner, which is having the desired effect. it is conceivable that.

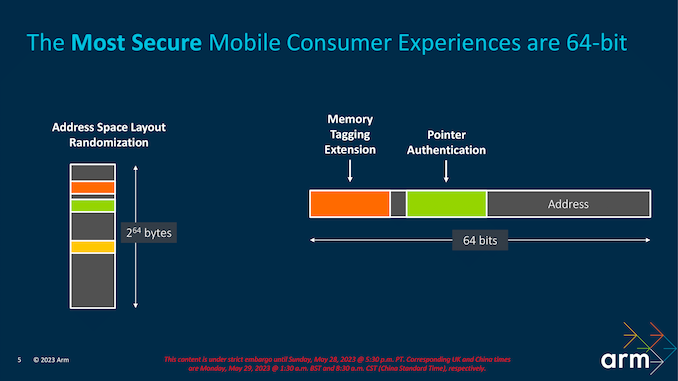

Arm used Memory Tagging Extensions (MTE) (Armv8.5) to improve security in early Armv9 architectures. This is a hardware-based implementation that uses Pointer Authentication (PA) extensions to protect against memory vulnerabilities. Memory-based vulnerabilities have been a consistent threat to hardware-based security for years, and Arm continues to develop within his IP to mitigate these types of attacks. For reference, Google’s Chromium project claims that about 70% of high-severity bugs are memory-related.

One of the security features associated with the latest Armv9.2 architecture is the introduction of the new QARMA3 Pointer Authentication Code (PAC) algorithm. Arm claims the new algorithm cuts his PAC’s CPU overhead to less than 1% of his, even with a small core, giving developers and handset vendors even less reason not to enable security features. increase. Most of these improvements revolve around hardware integrity and security, combining his MTE and native advantages with 64-bit instructions and architecture, all looking towards 2023 and beyond for device safety. designed to further enhance This fits with Arm’s philosophy of encouraging a full transition from the 64-bit/32-bit hybrid market to 64-bit.

Finally, when it comes to performance, Arm claims that the complex architecture of its latest generation CPUs and cores has definitely improved power efficiency. At equal performance, the Cortex-X4 reduces power consumption by more than 40% compared to his Cortex-X3, while the Cortex-A720 and A520 save him 20-22% over their respective previous generations. As for the DSU-120 hub itself, Arm claims power efficiency has improved by 18%.

Of course, most of these power savings are going to be invested in better performance. But it does show what SoC and handset vendors can aim for this generation if they just focus on power efficiency and battery life.