PCI Express 7.0 Spec Hits Draft 0.3, 512GBps Connectivity on Track For 2025 Release

In what is fast becoming a very busy week with data center and high-performance computing news, the PCI Special Interest Group (PCI-SIG) hosts its annual developer conference in Santa Clara. The annual gathering of the industry’s leading expansion bus developers and ecosystem members offers many technical sessions for hardware developers, but for outsiders the most important news to get at the show is , which tends to be the annual update of the SIG. Ecosystem. This year was no exception, with updates on the development status of PCIe 7.0, PCIe 6.0 adoption and cabling efforts.

With PCI Express 6.0 completed early last year, the PCI-SIG quickly moved to begin development work on the next-generation PCIe 7.0, which was announced at last year’s developer conference. Aimed for release in 2025, PCIe 7.0 again doubles the bandwidth available to PCIe devices, delivering up to 16 GB/s full-duplex bi-directional bandwidth on a single lane, overcoming the popular x16 We aim to reach up to 256 GB/s in the slot. each direction.

| PCI Express bandwidth (Full Duplex: GB/s/direction) |

||||||||

| slot width | PCIe 2.0 (2007) |

PCIe 3.0 (2010) |

PCIe 4.0 (2017) |

PCIe 5.0 (2019) |

PCIe 6.0 (2022) |

PCIe 7.0 (Estimated by 2025) |

||

| ×1 | 0.5GB/s | ~1GB/s | ~2GB/s | ~4GB/s | 8GB/s | 16GB/s | ||

| ×2 | 1GB/s | ~2GB/s | ~4GB/s | ~8GB/s | 16GB/s | 32GB/s | ||

| ×4 | 2GB/s | ~4GB/s | ~8GB/s | ~16GB/s | 32GB/s | 64GB/s | ||

| x8 | 4GB/s | ~8GB/s | ~16GB/s | ~32GB/s | 64GB/s | 128GB/s | ||

| ×16 | 8GB/s | ~16GB/s | ~32GB/s | ~64GB/s | 128GB/s | 256GB/s | ||

Early work on PCIe 7.0 was just beginning when it was announced last year. For the 2023 conference, the PCI-SIG has completed the release of the specification’s first draft version, version 0.3, ready for distribution to members of the group, marking the next step in standards development.

Early drafts of PCI-SIG standards tended to skimp on published technical details, and PCIe 7.0 v0.3 is no exception. As a result, there is little new to know about the specification itself, other than the goals announced last year that have yet to be outlined.

Still, the completion of the first draft of the specification is significant because it shows the group’s success in developing the core technical foundation needed for faster PCIe communications. Given that PCIe 7.0 required doubling the bus frequency at the physical layer, and in PCIe 6.0 he was a major development circumvented by PAM4 signaling, this is no easy task. Still, nothing comes for free when it comes to improving data signaling, but with PCIe 7.0 the physical layer needs to be improved once more, so the PCI-SIG will definitely return to hard mode development. This time, about 30GHz.

Electrically, PCIe 7.0 uses PAM4 + FLIT encoding, just like its predecessor. Therefore, most of the physical layer development costs will be saved in logical layer development in the next standard.

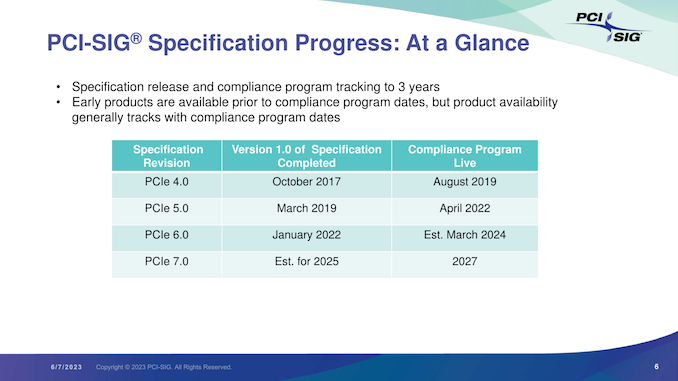

Ultimately, PCI-SIG’s standard pace is based on a three-year development cycle. As a result, this year’s draft announcement came on schedule for a group expected to develop for another two years. If the rest of the drafting work goes smoothly, the PCI-SIG plans to complete the PCIe 7.0 specification in 2025.

The compliance program for this specification is scheduled to go live in 2027. A compliance program is a functional barometer of hardware availability, as compliance testing and certification is effectively required before large-scale commercial hardware using a new specification is shipped. . And, with a few exceptions, they tend to take 2-2.5 years to assemble. All of this means that the first commercial PCIe 7.0 product isn’t expected until at least 2027, which is his five years from now, and we’re still working towards PCIe 7.0 following this early draft. It emphasizes that a lot of work is needed.

PCIe 5.0/6.0 cables coming in late 2023

While PCIe 7.0 is in the works, the first hardware for PCIe 6.0 is still in the works, and even PCIe 5.0 gear is less than a year out in the wild. Therefore, in parallel with the development of the core specification, the PCI-SIG is also working on some auxiliary areas of the completed specification, especially cabling.

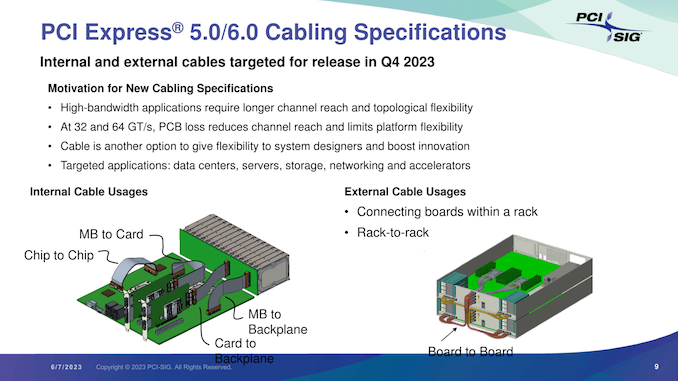

We’ve traditionally thought of PCIe as a bus that runs on a printed circuit board first and foremost, but the standard has always allowed cabled connections as well. And PCI-SIG actually expects the new standard to increase the use of cables in servers and other high-end devices because of PCB channel reach limitations and worsening with higher signal frequencies. So, new technologies and new materials are giving rise to new options for better cables, giving cabling a new look as options to maintain/extend channel reach in line with the latest standards. It is

To this end, PCI-SIG is developing two cable specifications, which will be ready for release in the fourth quarter of this year. This specification covers both PCIe 5.0 and PCIe 6.0 (because the signal frequencies are unchanged) and includes specifications for both internal and external cables. Internal cabling is for connecting devices to other parts of the system (both devices and motherboards/backplanes), while external cabling is used for connections between systems.

In terms of signal technology and absolute signal speed, PCI Express is about a generation behind Ethernet. This means that much of the early development on high-speed copper signaling is already being undertaken by Ethernet workgroups. So while work is still needed to adapt these techniques to PCIe, the underlying techniques are already proven and will help simplify PCIe standard development and cabling a bit.

Overall, cable development is clearly more of a use case for server technology than what we see in the consumer space. However, cabling standards will continue to be an important development, especially as enterprises continue to piece together ever more powerful systems and clusters.