TSMC Preps 6x Reticle Size Super Carrier Interposer for Extreme SiP Processors

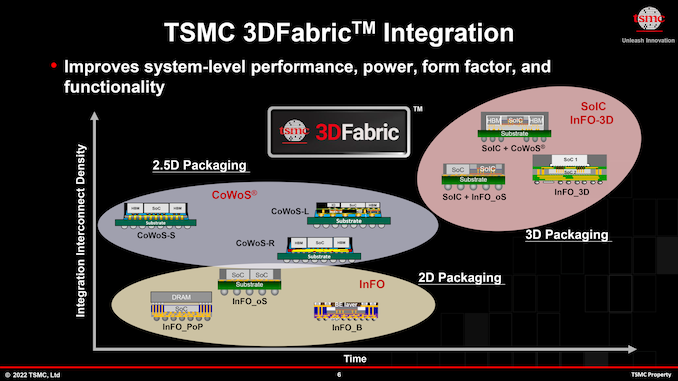

As part of its efforts to push the limits of the largest manufacturable chip size, Taiwan Semiconductor Manufacturing Corporation is working on a new Chip-on-Wafer-on-Substrate L (CoWoS-L) packaging technology. Larger super carrier interposer. Targeting a 2025 timespan, TSMC’s next-generation CoWoS technology will allow the interposer to reach from 3.3x to up to 6x TSMC’s maximum reticle size. These powerful System-in-Packages (SiPs) are intended for use in performance-hungry data center and HPC chips. These niche markets have proven willing to pay a hefty premium to put multiple high performance chiplets in one package.

Yujun Lee, business development director in charge of TSMC’s foundry’s high-performance computing business unit, said at the company’s European Technology Symposium 2023, “We are currently developing CoWoS-L with a 6x reticle size using supercarrier interposer technology. We are developing the technology,” he said. .

Global megatrends such as artificial intelligence (AI) and high-performance computing (HPC) are creating demand for seemingly limitless computing power. That’s why companies like AMD, Intel, and NVIDIA are building highly complex processors to support these AI and HPC applications. . One way to increase the computational power of a processor is to increase the processor’s transistor count. These days, companies are using multi-tile chiplet designs to do this efficiently. Intel’s impressive 47-tile Ponte Vecchio GPU is a good example of such a design. But TSMC’s CoWoS-L packaging technology will allow foundries to produce supercarrier interposers for even gigantic processors.

EUV reticle theoretical limit is 858mm2 (26 mm x 33 mm) So using 6 of these masks allows for a SiP of 5148 mm.2. A massive interposer like this not only gives room for multiple massive computing chiplets, but also leaves plenty of room for things like 12 stacks of his HBM3 (or HBM4) memory. This means a 12288-bit memory interface with a bandwidth reaching 9.8. TB/sec.

“The SuperCarrier interposer features multiple RDL layers on the front and back of the interposer to increase yield and manufacturability,” Li explained. “We can also integrate various passive components into the interpreter to improve performance. This he CoWoS-L of six reticle sizes he plans to be certified in 2025.”

Building 5148 mm2 SiP is such a daunting task that one can only wonder how much it will cost and how much developers will charge.Currently, NVIDIA’s packaging for his H100 accelerator spans multiple sizes of interposers, but costs around $30,000. So a significantly larger and more powerful chip could push the price even higher.

But paying for big processors isn’t the only big investment data center operators need to make. Active silicon amount 5148mm2 What can be housed in a SiP will almost certainly be some of the most power-hungry HPC chips ever made, and the chips will also need powerful liquid cooling to match. To this end, TSMC revealed that it is testing on-chip liquid cooling technology and said it has successfully cooled the silicon package at power levels as high as 2.6kW. Therefore, TSMC has some ideas in mind to address the cooling needs of these extreme chips, even at the cost of integrating even more cutting-edge technology.